CMOS SoC Spectrometer for Sub-mm Wave Astronomy

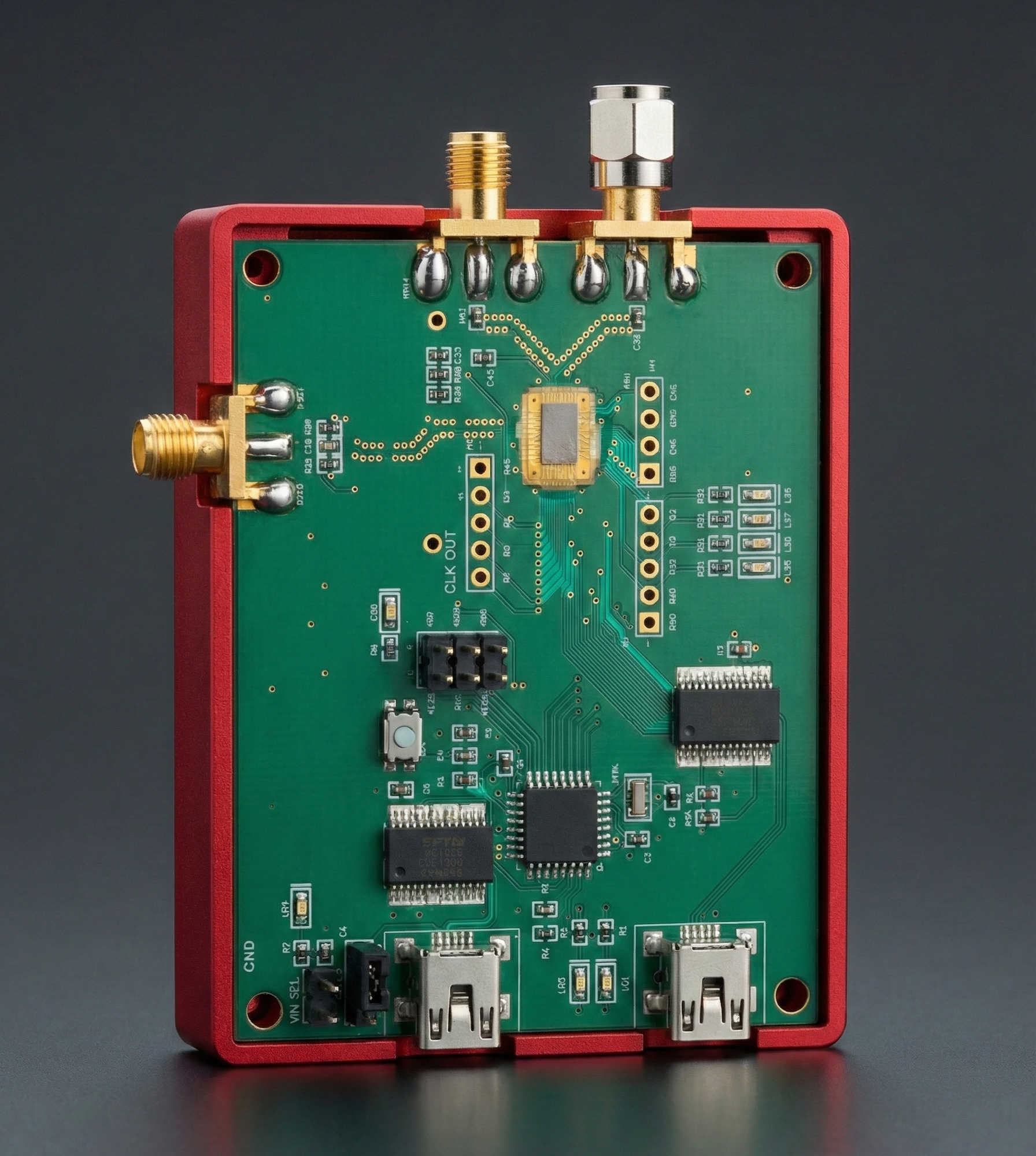

System-on-Chip (SoC) CMOS spectrometers are in high-demand as a method to replace power-hungry FPGAs in RF astronomy. In the strict energy budgets of CubeSats and deep-space probes, every watt counts, and this novel chip (developed by JPL/UCLA) promised to slash power consumption by an order of magnitude—but only if it could prove its stability and precision in the real world.

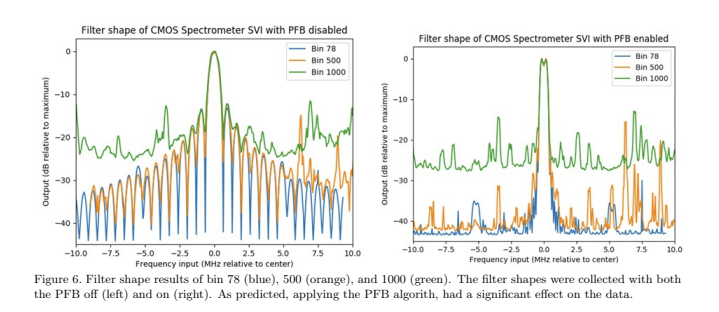

I was tasked with validating the SVII SoC spectrometer designed by Adrian Tang of JPL, as it was the first version that had performance specs useful for astronomers. I designed and built a rigorous hardware characterization bench from scratch. I subjected the prototype chip to a battery of stress tests, measuring its long-term stability (Allan Variance) and spectral resolution under various operating conditions. I specifically targeted edge cases, sweeping clock power levels and toggling the Polyphase Filter Bank (PFB) to map the device’s true performance envelope versus its theoretical design.

The testing revealed that while the chip was flight-capable, it had a hidden sensitivity to clock signal power—a non-linear behavior that could have jeopardized a mission if left undiscovered. My analysis provided the critical feedback loop needed by the chip designers at JPL, confirming the architecture’s viability while pinpointing the exact operational constraints for the next hardware revision.

This project honed my ability to take experimental "black box" hardware and rigorously qualify it for flight. By translating theoretical specs into empirical reality, I helped mature a technology that will allow future missions to deploy massive focal-plane arrays without blowing their power budgets.